高速A/Dコンバータ(ADC)による変換後のデジタルデータがラズベリーパイI/Oポートの遅れによる、デジタル値読み取りミスを防ぐためにFPGAを一時キャッシュとして利用する。

2. 方法

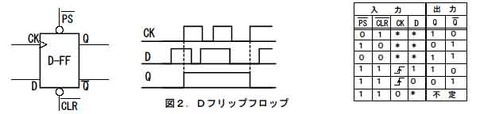

一時キャッシュの方法として今回は、簡単に構成可能なDフリップフロップを使用する。

Dフリップフロップの回路並びにタイムチャートを図1へ示す。

図1. Dフリップフロップの回路図とタイムチャート

今回は、XiilinxのISE上で構成したため図1にある、~PS,~CLK,~Q(~はインバーテッド)は省略した。

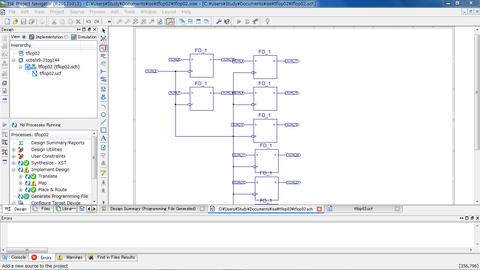

ADCからの出力は各ピンごとに1bitづつ配置されているため、今回はFPGAにも同様の1ポートにつき1bitづつ配置した。

XilinxのISEを用いてFPGAに各ポートにDフリップフロップを構成した。

今回は学習のため、verilogを使用せずschematic(回路描写)による論理合成を行った。

図2. 回路図

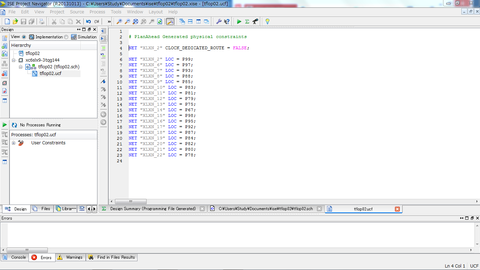

図3. 回路のピン配置

3. 結果

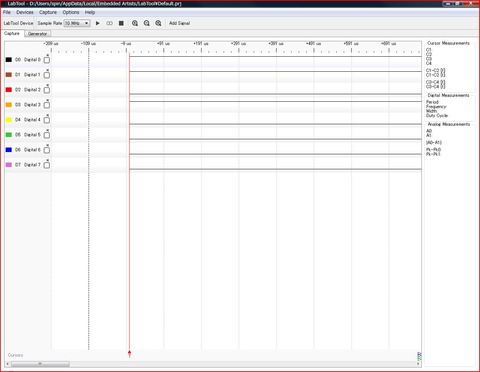

ロジックアナライザーを用いて下位4bitの動作を確認した。

図4. ロジックアナライザによるDフリップフロップの動作確認

4. 今後の課題

構成したDフリップフロップが要求する速度で動作するのかを検証する。