1. ダウンロード及びインストール

はじめに、XilinxのダウンロードページよりISE(Integrated Software Environment)をダウンロードしてくだい。

※約2GB×4個ほどあるので根気強くダウンロードしましょう。

ダウンロード後、解凍、インストールは他サイトを参照してくだい。

今回は無償版のWeb Packをインストールします。

(Web Packは一部制限がありますが開発をする上で特に問題はないと思います。)

2. プロジェクト作成

今回はISE 14.7を使用します。

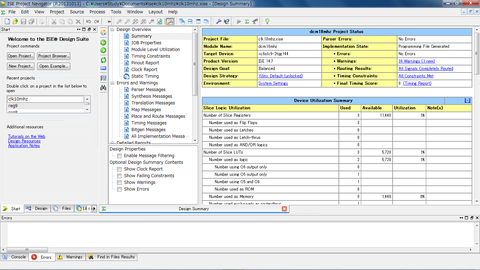

図.1はISEを起動したものです。(今までに個人的に使用しているため様々なものが混在しています。)

左上のFile→New Project...または、New Projectボタンから新規プロジェクトウィザードを開始します。

図1. ISE起動画面

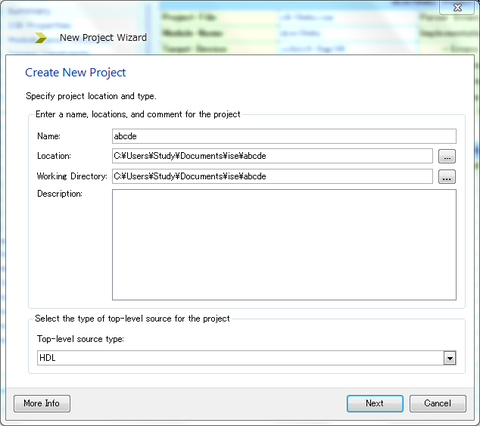

ウィザードが始まると、図.2の画面が現れます。

Nameには適当な名前を入力します。(稀にですがこういうソフトは日本語入力(全角)を使うとコンパイル時などにエラーが出ることが経験上よくありますので、ローマ字(半角)入力をお勧めします。)

Location,Working Directoryにはプロジェクトや生成ファイルの保存先を指定します。(この際もnameの時同様、半角をお勧めします。)

図2. プロジェクトウィザード

今回はabcdeというプロジェクトを作成します。

Top-level source typeにはHDL(Hardware Discription Language)またはSchematic(回路描写)を選択します。今回はHDLを選択しNextを押します。

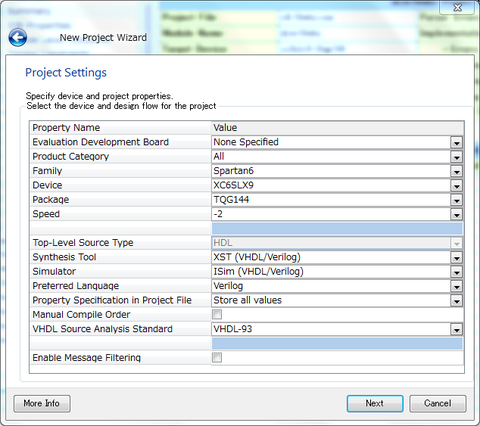

次に使用するボードの詳細を設定します。

今回はPapilio Duoを使用するので図.3の設定となります。

図3. ボード設定

設定後、Nextを押します。

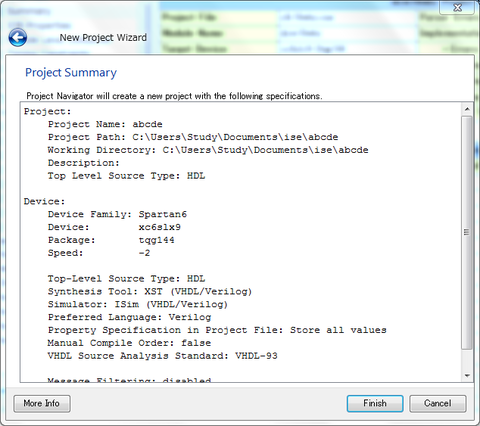

最後に図.4プロジェクトの確認画面が現れるのでFinishを押してプロジェクトを作成します。

図4. プロジェクトの設定

3. ソースファイルの作成、プログラミング

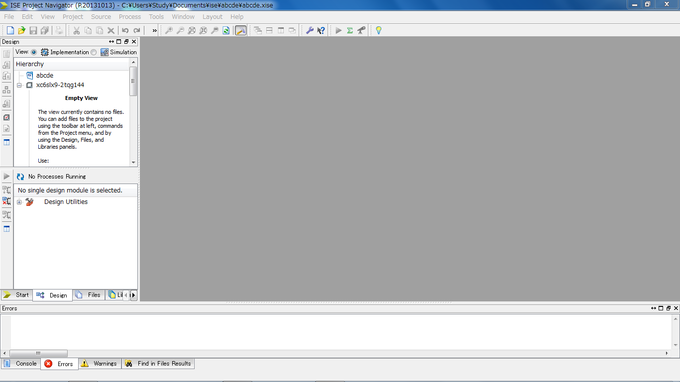

プロジェクトの作成が終わると図5のような画面が現れます。

図5. プロジェクト作成後の画面

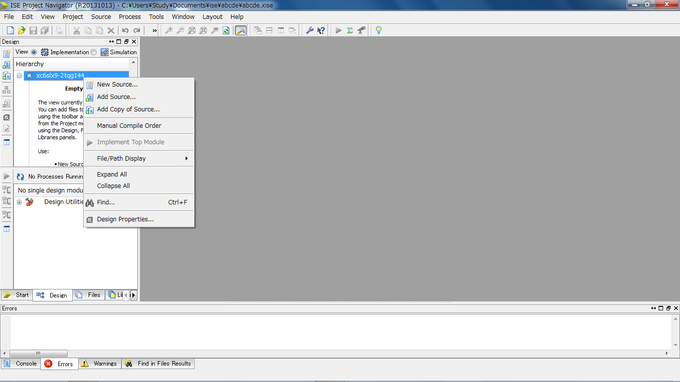

次に作成したプロジェクトの下にある搭載チップ名(ここではxc6slx9-2tqg144)を右クリックします。

すると、図6のような画面が出てきます。一番上のNew Source...をクリックしてソースファイルを作成します。

図6. チップ名の上で右クリック

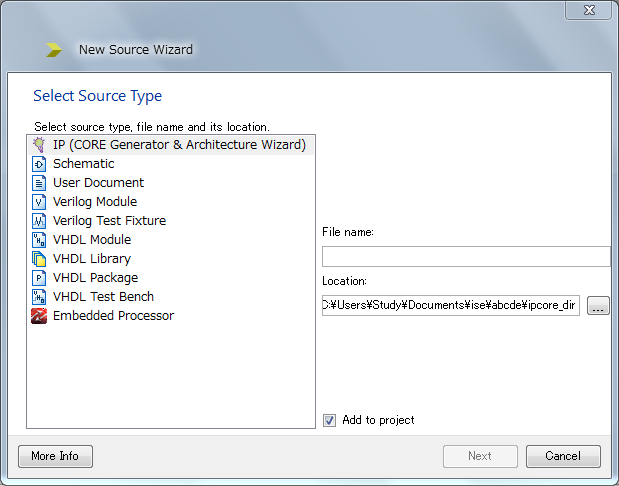

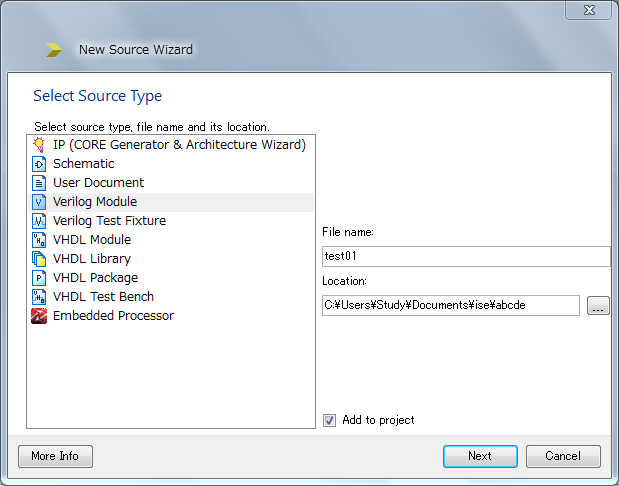

すると図7の画面が現れます。

図7. ソースファイル等作成ウィザード

今回はverilogによる回路構成を行うのでVerilog Moduleを選択します。

またその際にプロジェクト作成時同様に名前を決定します。ここではtest01というソースファイル名にします。Locationは恐らく最初に作成したプロジェクト内に保存するようにデフォルトでセットされています。また、Add to projectのチェックは必ずつけてください。設定後、次へ進みます。

図8. Verilog Moduleの追加

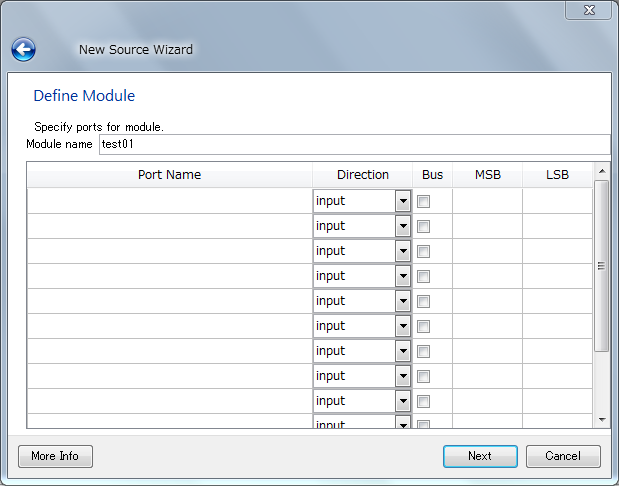

すると図9のような画面が現れます。これは入出力ポートの設定及び設置です。Port Nameに任意の名前、Directionに入出力の指定などの設定及び設置が行えますが、ここでポートを記述する必要はなくここで記述を行うメリットとしては、雛形にコンピュータ側がただ単に入力をしてくれる、ただそれだけです。私の場合はここではポート設定を行わず手動で書き込んでいます。

図9. ポート設定

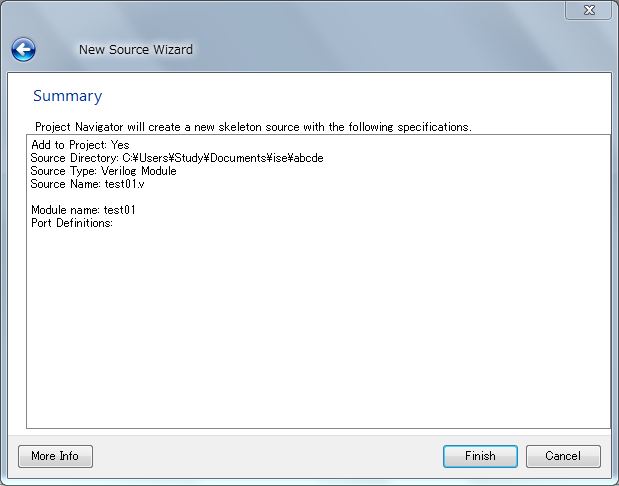

次へ進むと確認画面が現れます。

図10. 確認画面

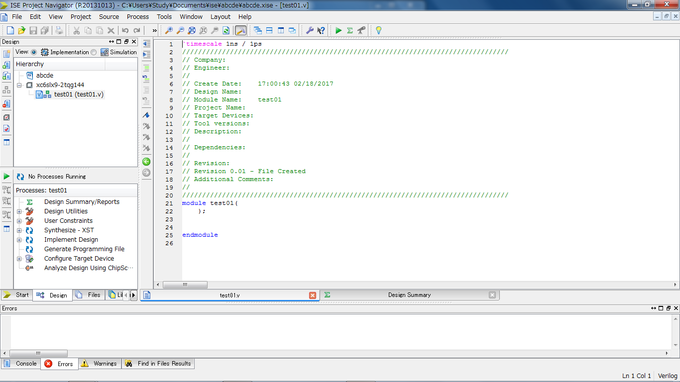

Finishを押し完了すると、図11の画面に戻ります。

すると、チップ名(今回はxc6slx9-2tqg144)の下に新たにtest01(test01.v)というファイルが現れたかと思います。

図11. メイン画面